導入課題の目的は,論理システムの講義および実験2ハードウェアの復習を含めた,HDL設計とCADツールの習熟である. また,適切なレポート(報告書)の書き方について特に重視する.

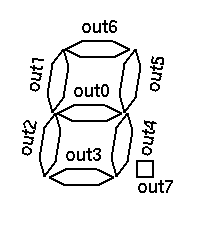

7SEG LED(下図)は16進数のA〜Fを含む数値の表示のためによく利用されるデバイスである. このデバイスは,8つのLEDから構成される.

通常,7SEG LEDはデコーダとセットで利用され,1桁の16進数(4ビット)の入力を受けて0〜Fを表示する. しかし,実験3ハードウェアで使うPowerMedusaボード上の7SEG LEDは,16進数の表現以外の用途にも利用できるように,あえてデコーダは準備されていない. そのため,FPGAの出力は7SEG LED中の8個のLEDそれぞれにつながっている.

本課題では,この1桁の16進数(4ビット)の入力を受け,MU500-RK上(MU500-7SEG上ではない)の8個のLEDを適切に点灯させて0〜Fを表現する組合せ回路を設計する. また,この回路を部品として用いてカウント値を表示する順序回路を設計する.

PowerMedusa上の入力装置から4ビットのデータを入力し,MU500-RK上の7SEG LEDに1桁の16進数を表示する回路を設計し,ボード上で動作を確認せよ.

まず,7SEG LEDを用いて1桁の16進数0〜Fを表現するため,その表現方法を考える. 例えば,"1"の表現は下の図のようになる.

レポートには,0〜Fをどう表現することとしたか,などを記述する.

1桁の16進数は4ビットで表される.

4ビットを入力とし,下図のように7SEG LEDを駆動する8ビットの信号を出力する組合せ回路を設計する.

レポートには,どのように論理回路を設計したかの方針を,必要に応じてHDLコードの説明を交えながら示す.

ボード上の入力装置から4ビットを入力し,7SEG LEDに1桁の16進数を表示するよう,入出力ピンを指定する必要がある.ピンアサイン表を参照のこと.入力装置は自由に選んでよい.

レポートでは,設計の方針(使用した部品,ピン指定など)について説明を加える.

まず,設計した回路がシミュレーションによって正しく動作することを確認する.

次に,回路をFPGAにダウンロードし,正しく動作することを確認する.

レポートでは,動作確認の方法(テストベンチコードを交えてよい),正しく動作した(あるいは動作しなかった)ことを報告する.

回路サイズや動作可能速度などの性能を評価する.

この評価結果について,十分なものであるかや改善指針などの考察を与える.

10進数4桁の数字を表示して一定の間隔で1ずつカウントアップする回路を設計し, ボード上で動作を確認せよ. 設計した回路のサイズ(使用Logic Element数),動作可能速度(最大クロック周波数)などの性能を調べよ.

課題2の回路にボード上のスイッチからの入力を追加し,スイッチを押す度にカウントアップを停止/再開できるようにせよ.

TA用レポートチェックシート (txt形式,UTF-8)

つまり提出されたレポートでは,この項目が満たされていることを期待する.