よくある質問とその答え(FAQ: Frequency Asked Question)

新しく追加した項目,以前から存在していた項目に追記および変更した部分は,しばらくの間,[New]で表示します.

FAQのさらにFrequentlyな項目には,[Check]で表示します.

スケマ設計や旧ボードのみに関係する項目もありますが,しばらくそのまま残しておきます.

こびっどさん対応2020で関係ない/異なる項目もありますが,適宜で読み替えてください.

目次

|

|

- 実験の進めかた

- 設計/デバッグ

- PowerMedusaボード

- その他

|

- 2023年度の新教育システムではQuartusは/opt/intelFPGA/20.1/quartus/bin/quartusで起動します.長くて打つのが大変なので,パスを通しましょう. $ export PATH="$PATH:/opt/intelFPGA/20.1/quartus/bin" これでquartusと打つだけで起動できます..bashrcなどに書いておきましょう.

- ちなみに $ quartus & のように&をつけるとバックグラウンドで動かすことができ,起動後に別のコマンドを実行することができます.つまりシェルは子プロセスをforkし,そのコマンドが完了するのを待たないということです.

- Tool, License Setup ...からライセンス設定を起動し,"License file:" に "27003@is-fpg-10" を入れる.これでもだめなら教員を呼ぶこと.

- modelsim_ase を使って下さい.「ModelSim によるシミュレーション」ページの「設定」の項目の最後を参照のこと.

- QuartusII のライブラリ検索パスに大量のファイル,または,日本語ファイル名のファイルが入っている.

- プロジェクト名,デザイン名はasciiにして下さい.アルファベット,数字,"_" 以外の文字はおすすめしません.

- 作業ディレクトリ内に日本語ファイル名のファイルを置かないで下さい.

- ホームディレクトリ自体を設計ディレクトリにせず,必ず専用のディレクトリを作ってその中で作業して下さい.

(でないと,"." で始まる大量のファイルやら "ドキュメント" ディレクトリやらを QuartusII が取り込みに行って落ちます.)

- compiz が動いていると MegaWizard が固まります.

デスクトップの [システム]→[設定]→[外観の設定] で [視覚効果]タブで「効果なし」に設定して下さい.

- 主記憶用のRAMの作り方の冒頭にも書いていますが,MegaWizardの画面表示が小さいと操作の途中で固まります.立ち上げてからまずスクロールバーが消えるくらい画面を大きくすると解消できるようです.不思議です.

いったん固まってしまったら, $ ps して mega_* を kill してください.

- Web Browserを設定して下さい.

Tools→Options... から Internet Connectivity タブで "Web browser" に export/share/bin/firefox を設定します.

- ちゃんとコンパイルされていない.

- ちゃんとコンパイルされていないとピンは指定できません.

もう一度,コンパイルしてみてください.

- デバイスの設定は合っていますか?Cyclone IV E EP4CE30F23I7です.

- FPGAのピンにアサインできるのは,Top-Level EntityのBlock Diagramの

入出力だけです.FPGAのピンにアサインしたい入出力は,

Top-Level EntityのBlock Diagramまで引っ張ってきましょう.

- 1つのプロジェクトの中で,複数のFPGA用データを

作ろうとしていませんか?

別のFPGA用データを作るのでしたら,新しいプロジェクトを立ち上げてください.

トップのBlock Diagramのファイル名がプロジェクト作成時に

していたTop-Level Entityと同じでないと,

コンパイルがうまくいきません.

解決方法(いずれかの方法を取ること)

- Block Diagramのファイル名をTop-Level Entitiyと同じに変更する.

- Project Navigatorで"Projectを右クリック→Settings→Generalで

Top-Level Entity"をトップのつもりで編集していたBlock Diagramのファイル名に変更する.

- Project NavigatorのFilesタブでファイルを右クリックし,Set as Top-Level Entityとする.

- バスを配置し幅と名前を定義する.

- 名前は"バスを選択して右クリック→Properties→General→Name"でつける

- この時,バスの名とバスがつながるピンの名が同じだと

コンパイル時にエラーが起きる.

- 名前はname[xx..0](xxはバスの幅-1)の形でつける.

- バスをつなぐ入出力ピンも同じ書式で名前をつける.

- "0"を"00","1"を"01"とか書くと,コンパイル時に怒られますので注意しましょう.

- バスに配線をつなぐ

- 配線を選択して右クリックし,

"Properties→General→Name"に引き出す配線を明示する.

- バスがA[15..0]であり,9bit目を引き出すのであればNameに"A[9]"と入れる.

- "A9"と大括弧を省いて書くとコンパイル時に認識されません.線がつながってない等,別の理由で怒られます.

- バスとバスを合流/分岐させることもできます.

A[7..0]とB[15..8]を定義して合流させ,C[15..0]にすることができます.同様に分岐もできます.

※[0..15]と[15..0]ではバスのbit順が逆になります.実験で使っているCADの仕様で,RAMからの出力が[15..0]の順序なので,こちらに統一しておくのがよいでしょう.

シフタの製作時に,バスA[15..0]のA[0]とバスB[15..0]のB[1]を

つなぎたいことがあるかもしれません.

この時,バス間の配線を直線で引いてしまうと,

その配線には1つのプロパティしかつけれないので,うまくつなげません.

この場合,配線の途中にバッファを置いて配線を分割し,

バスA[15..0]につながっている部分にA[0],

バスB[15..0]につながっている部分にB[1]のプロパティを与えることで実現できます.

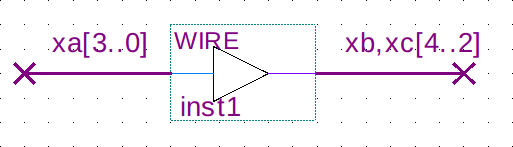

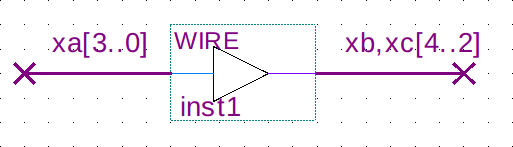

バッファには色々種類がありますが,

単純に配線を名前を変えたい場合は,"wire"のバッファを使えば良いでしょう.

"wire"はバス間もつなげます.複数の配線をバスとして束ねるには,","で区切った名前のリストをバスに貼り付けます.例えば下図のようにできます.

デバッグ用に途中の配線に出力ピンを追加し,

それを用いて観測して下さい.

一応,"Insert Node or Bus→Node Finder→Customize"で,

Filterを"Design Entity (all name)"にしてOKを押し,

さらにListを押すと,全インスタンスの出力等も

候補に出てきます.しかしながら,通常,

これらの観測点はコンパイル中の最適化によって

消えてしまうことが多いため,

QuartusII自体がデバッグ用の出力ピンを

追加することを勧めています.

- ファイルの読み出し権限がない

エクスプローラ等でファイルを右クリックし→プロパティ→セキュリティで,

自分に読み出し権限があるかどうか調べる.

無ければ,必要に応じて変更する(他人のファイルなら「してもらう」).

- ファイルが壊れている

過去にCADが保存時にファイルを壊してしまったと思われるケースがありました.

この時は,メモ帳で対象ファイルと他の無事に開けるファイルを開いて見たところ,

開けないファイルは後ろの方の書式がおかしくなっていることが確認できました.

一般的なソフトウェア同様,CADにもバグはあります.

受講上の注意の最後にあるように,

ファイルは適時バックアップして,このような状況に備えて下さい.

上記にあるように,CADもソフトウェアですのでバグはあります.

CADの動作が時々おかしくなるという報告もあがっています.

このような時には,一度CADを終了して,再度立ち上げなおして動かしてください.

変な動作らしきものの例

- FPGAボードへのダウンロード時に,再コンパイル前の.sofが送られているようで,

動作を変更した部分が反映されない.

- シミュレーションの入力ファイルを変更したのに,どうも変更前のファイルで

シミュレーションを行っているようだ.

"Assignments→Settings...→Libraries"を選択後,インクルードしたい

回路があるディレクトリを選択し,Addボタンを押します.

そうすれば,ライブラリの呼び出し時の一覧に上記のディレクトリが追加されます.

"Help→Message List"でCADのメッセージの解説(英語)を見ることができます.

ここで調べて下さい.

- バス/配線/ファイル名等に記号が入っていませんか?

記号によってはCADが認識してくれないものがあります.

現状では,以下の記号が大丈夫/だめということが分かっています.

- 大丈夫なもの: ハイフン,アンダースコア

- だめなもの: 小括弧,中括弧

- CADは大文字小文字を区別してくれませんので,

大文字と小文字を変えると同じになる名前はつけてはいけません.

- 設計した回路ブロックに既存の論理素子などと同じ名前をつけると,

呼び出しがうまくいかなくなるので,名前はかぶらないようにして下さい.

- バスに同じ名前をつけると,同じ名前をつけた配線同士を

接続したいものとして処理されます.

便利な機能ですが,気がつかないうちに

余計な所で接続されることがあるので,気をつけて下さい.

Tools->Options->Generalで,

"Display tabs for child windows"をチェックすると復活します.

QuartusII は,与えられたタイミング制約の下でハードウェア資源を最小化します.

制約をかけないと遅い (しかし小さい) 回路が合成されますので,適切な値を設定して下さい.

- トップレベルが順序回路の場合

- 上記の Create Clock 等で設定したクロック周期が合成時の制約になります.

- TimeQuest のレポートの Unconstrained Paths と Unconstrained Clocks が 0 になっているのを確認して下さい.

- Input, Output 関係の unconstrained も消したければ,SDC で set_input_delay, set_output_delay を設定して下さい.

例:

set_input_delay -clock {clk20MHz} 0 [all_inputs]

set_output_delay -clock {clk20MHz} 0 [all_outputs]

- トップレベルが組合せ回路の場合 (サブモジュール単体のチューニング時など)

- SDC で set_max_delay を設定して下さい.

例:

set_max_delay -from [all_inputs] -to [all_outputs] 10

- その他,TimeQuest 関係の設定

- PLL を使う場合

- SDC に derive_pll_clocks が書かれているか (あるいは他の方法で generated clock を指定しているか) 確認して下さい.

(無いと "PLL cross checking found inconsistent PLL clock settings ..." の警告が出ます.)

- マルチサイクルパスがある場合

- lサイクルで計算が完了する必要がないパス (2サイクル後に使うデータの計算など) が動作周波数を制限している場合,set_multicycle_path で指定して下さい.

(パイプライン動作を考えると1サイクル毎にレジスタをはさむほうが安全です.)

- Clock Uncertaintity の警告が出る

- SDC に derive_clock_uncertainty を書いて下さい.

Compilation Report に回路サイズ,動作速度などの見積もりが出ています.

- 回路サイズ

Fitter - Summary に Total logic elements が出ています.100% を超えるとチップに入りません.

- 動作速度

TimeQuest Timing Analyzer - Fmax Summary に最高動作周波数が出ています.

設計によってはクロックの設定が必要です.

- チップのクロック入力を直接フリップフロップのクロックに入れていない場合,どの線をクロック信号として扱うかツールに教える必要があります.

(PLLを使う場合は自動的に認識されるようです.)

- Tools - TimeQuest Timing Analyzer の Constraints - Create Clock, Create Generated Clock で設定します.Targets のところが信号線名です.

- Assignments - TimeQuest Timing Analyzer Wizard から設定してもいいです.

Setup Summary などの項目が赤で表示されていたら,与えたクロック周波数に回路が間に合っていません.

どこがクリティカルパスになっているかは,Worst-case Timing Paths の情報を参考にして下さい.

- 動作速度 (クロックが複雑な場合)

フェーズ毎のクロック信号を論理で作るなど,複数クロックがある設計(おすすめしません)では,全てのクロック相当の信号線を create_clock または create_generated_clock で指定して下さい.

この場合,複数のクロックが関係するパスはFmax Summaryに反映されないことがあります.

Fmax Summaryと合わせて,Setup SummaryのSlackの値から動作周波数を判断して下さい.

組み合わせ回路の動作速度は遅延時間で確認をします。

Time Quest Timing AnalyzerのReport DatasheetsのPropagation Delay(遅延時間)から見ることができます。

Assignments -> Design Partitions Window または Tools -> Design Partitions Planner で design partition を設定できます.

- 一部のコードのみを書き換えて再コンパイルする際の時間が短縮できることがあります.設計が大きくなってコンパイルが遅くなってきたら設定するといいです.

- モジュール毎の回路サイズが分かります.レポートに必要ですよね.

- Design Partition Planner でモジュールの接続関係を表示できます.変なパスがないかのチェックに有用です.

- 境界での最適化が少し制限されるので,回路全体の性能は落ちることがあります.

(Assignments->Settings... の Compilation Process Settings -> Incremental Compilation で Ignore partition assignments during compilation をチェックすると全体を一括してコンパイルできます.)

慣れてくるとそうなりますよね.

- Quartus はコマンドラインから各フローを実行できます.

例:

quartus_sh --flow compile <プロジェクト名> (プロジェクトのコンパイル)

quartus_pgm <チェイン記述ファイル: 普通は output_files/プロジェクト名.cdf> (FPGA書き込み)

- ピン配置など設定は <プロジェクト名>.qsf にあります.テキストエディタで編集可.ツールは落としておいたほうが安心.

- ModelSim も同様です.オプション等は起動時のログを見るといいです.

- ところで,Verilog や SDC は,付属のエディタや gedit じゃなくて,大人用のエディタで書いてますよね.

Quartus Prime Lite Editionを手に入れ,自宅で作業を行う

- 演習で使用するバージョンは20.1です.無料で使用可能.

- 個別ファイルでインストールする場合は,少なくともCyclone IV device supportを入れる.

最終報告以降も実装を続け,デモができる程度に完成させて,

デモを行ってください.

実験期間終了後でも,平日昼間は計算機室を使えます.

平日昼間以外に計算機室を使用するつもりならば,

「時間外実験演習申請書」を提出し,

教官の許可を受けて計算機室を使用してください.

GitHub Classroom の共有リポジトリを利用してください.

バックアップから復元してください.

コンピュータのディスクが壊れたり,ソフトが異常終了して重要なデータを壊したり,

はたまた,操作ミスから空データで重要なデータを上書きしてしまうことは,

この先,コンピュータを使用する上で多々経験することでしょう.

そういった時のために,ちゃんとバックアップを取っておきましょう.

Gitプロジェクト,ブランチの管理ポリシーを決め,有効活用して下さい.

原始的ですが,USBメモリなどに時々保存しておくのも方法です.

組んだ相手(orグループor下請けor上司)が外れだったという不幸なことは,

長い人生の中では何回か経験することになるでしょう.

今回も,その中の1回が巡って来たとして,

あきらめて,自分で相手の担当部分も自分で行い,帳尻合わせをしましょう.

幸い,ここは大学ですので,企業のように,

「相方が出てこなくなろうが何だろうが,

ちゃんと期日までにきちんと仕事を終わらせて下さい.」

という厳しいことは言いません.

相方が出てこなくなったことを考慮して成績をつけます.

全ての命令を実装できなくてもかまいませんから,

何とか,プロセッサと言える最低レベルのもの(メモリ・アクセス,

演算,条件分岐による制御が可能なもの)を作り,デモを行ってください.

PRN入力はプリセット入力です.動作は,クリア(CLR)入力の反対で,

信号が入力されるとD-フリップフロップの値が1になります.

ちなみに,このPRNとCLRは負論理ですので注意して下さい.

Help → Search で探して下さい.

各論理素子の説明は

Using HDL with the Quartus II Software → Primitives

にあります.

3状態バッファ(Tri-state buffer)なる素子があります.

これは,状態切替え用の入力により,以下の2つの状態を切替えることできる素子です.

- 信号線より入力された値をそのまま出力する

- 出力をハイインピーダンス状態にする.(出力側の状態は他の素子の出力で決まる)

信号が出力されると困る場合,この素子を使って信号を遮断して下さい.

余談ですが,「3状態」の由来は,出力の状態が「0/1/ハイ・インピーダンス」の3つを

取れることから名付けられています.

RAMの作り方の最後に書いたように,

Megafunctionで作ったRAMはアドレスを入力した後に

クロックを入れないとデータが出てきません.

どのようにしてクロックを入力するかは,

マルチサイクルの読み出しを行うとか,

逆位相のクロックを有効利用するとか考えて下さい.

RAMの作り方にも書きましたが,

SIMPLE仕様通りの 64k words が載せられるほどFPGAのエンベデッドRAMの容量が無いため,妥協してもらって構いません.

ソートプログラムでも 4096 words あれば十分でしょう.

EP4C30は540672ビットなので最大16 bits x 33792 words となります.

ここを見ましょう

演習室から運搬した際にボードが破損していることがあるかもしれません.また,設計した回路が意図通りに動作せずFPGAボードの不良を疑いたくなることがあるかもしれません.動作検証済みの回路イメージでボード動作を確かめることは,ハードウェア設計においても問題の切分けにとても有効です.

ボードの各モジュール動作を確認するための board_check.sof を用意しました.アクセス制限を掛けていますのでPandAにログインしてアクセスしてください.

使い方は下記のとおりです.

- Quartus Prime Programmerを単体で起動する

- Windows: スタート > Intel FPGA 20.1 ~~~ > Programmer

- Linux: $ ~/intelFPGA_lite/20.1/quartus/bin/quartus_pgmw &

- FPGAボードとPCをUSB接続し,FPGAボードの電源を入れる.

- Programmerの左上にある [Hardware Setup...] を開いて設定する

- Currently selected hardware: "[USB-Blaster USB-x]" を選択

- USB-Blasterが出てこない場合は,接続をチェックした上でドライバも確認

- Closeをクリック

- Programmer の左側にある [Add File] を開いて設定する(メニューバーの Edit > Add File... でもよい).

- ダウンロードしてきた board_check.sof を選択する

- [Start] でFPGAに書き込む.右上のProgress:が"100% (Successful)"で緑色になればおけ.

期待される動作はだいたい下記のとおりです.下記のモジュール名と番号はPowerMedusaユーザーズマニュアルのP.17 3.2 ブロック構成図を参照してください.

- クロック用ロータリースイッチSW2でLED D3〜D10点灯の回転速度が変化する

- SW2をFにした状態で1クロックスイッチSW3を押すとLED D3-D10が順に点灯する

- Dip SW SW26のA0〜A7は7セグメントLED A〜HのOn/Offに対応する

- Dip SW SW27のB0〜B7に応じて7セグメントLED A-Bの値が変化する

- テンキースイッチ SW4〜SW23を押すとブザーBZ1が鳴る.7セグメントLED G〜Hの値が変化する

- 上部の拡張ボード(MU500-7SEG)にある64個のLEDは順に回転して点滅する.

- ロータリースイッチSW24,SW25に応じて,上部の拡張ボード(MU500-7SEG)にある64個の7SEG LEDの表示が変化する

期待される動作が確認できなかった場合は,Slackかメールで速やかにスタッフまでご連絡ください.形あるものいつか壊れます.

すでにドライバをインストール済なのに,

再度ドライバのインストールを要求されることがしばしばあるようです.

その場合は,TAを捕まえて,Administrator権限でドライバを入れてもらって下さい.

こちらのページを参考にしてドライバをインストールしてください.

このUser Guideが公式資料です.特にSection 3を参照してください.

/etc/udev/rules.d/51-usbblaster.rules

にroot権限で下記を記入してください.(してあります)

# USB-Blaster

BUS=="usb", SYSFS{idVendor}=="09fb", SYSFS{idProduct}=="6001", MODE="0666"

BUS=="usb", SYSFS{idVendor}=="09fb", SYSFS{idProduct}=="6002", MODE="0666"

BUS=="usb", SYSFS{idVendor}=="09fb", SYSFS{idProduct}=="6003", MODE="0666"

# USB-Blaster II

BUS=="usb", SYSFS{idVendor}=="09fb", SYSFS{idProduct}=="6010", MODE="0666"

BUS=="usb", SYSFS{idVendor}=="09fb", SYSFS{idProduct}=="6810", MODE="0666"

上記が公式資料での記述内容ですが,うまくいかないようなら下記も試してください(Ubuntu 18.04.3以上だとこっちが良いようです。(Ubuntu 16.04でもこちらの方が良い場合もあるようです))

# USB-Blaster

SUBSYSTEM=="usb", ENV{DEVTYPE}=="usb_device", ATTRS{idVendor}=="09fb", ATTRS{idProduct}=="6001", MODE="0666", SYMLINK+="usbblaster/%k"

SUBSYSTEM=="usb", ENV{DEVTYPE}=="usb_device", ATTRS{idVendor}=="09fb", ATTRS{idProduct}=="6002", MODE="0666", SYMLINK+="usbblaster/%k"

SUBSYSTEM=="usb", ENV{DEVTYPE}=="usb_device", ATTRS{idVendor}=="09fb", ATTRS{idProduct}=="6003", MODE="0666", SYMLINK+="usbblaster/%k"

# USB-Blaster II

SUBSYSTEM=="usb", ENV{DEVTYPE}=="usb_device", ATTRS{idVendor}=="09fb", ATTRS{idProduct}=="6010", MODE="0666", SYMLINK+="usbblaster2/%k"

SUBSYSTEM=="usb", ENV{DEVTYPE}=="usb_device", ATTRS{idVendor}=="09fb", ATTRS{idProduct}=="6810", MODE="0666", SYMLINK+="usbblaster2/%k"

こちらのページを参考にしてください.

このUser Guideが公式資料です.特にSection 3を参照してください.

トラブルシューティングとしてさらにこの辺りも参考になりそうです.

- jtagd (USB-BlasterのJTAG接続のためのプロセス) がJTAGをロックした状態でゾンビ化することがあるようです.こうなると新しいプロセスがJTAGを利用できません.

再現性が掴めていませんので,どういった時に発生したか教えてもらえると嬉しいです.いま把握している状況は下記のとおりです.

- PCとボードを接続してからProgrammerを立ち上げたら発生した

- 対処法は下記のいずれかです.

- $ ps x | grep jtagd で該当するプロセスを殺す

- 何も考えずに $ killall -9 jtagd を実行

- Programmer > Hardware Setup... > JTAG Settings で Local を選択してRemove Server,Programmerを一旦閉じてUSBを接続し直してから,再度Programmerを開いてHardware Setupし直す

- 上記のやり方が分からなければ,ゾンビが居なくなるまで気長に待つ

- いっそのことQuartusを再起動する

- なお,JTAGを確保できるプロセスは1つのみなので,Memory EditorとProgrammerを同時に立ち上げて接続しようとすると同様の症状に陥ることがあります.Programmerの立ち上げは必要最小限にしましょう.

- Assignments→Devices→Device & Pin Options→Configuration

→Use configuration deviceがチェックされており,EPCS1になっているか?

(デフォルトはAuto)

- Assignments→Devices→Device & Pin Options→Configuration

→Generate compressed bitstreamsがチェックされているか?

FPGAへのダウンロード時のファイル指定をする時,

"Error: Can't locate programming file hogehoge.sof (;) in Chain Description File"

というエラーが出て.pofファイルや.sofファイルを指定できないことがあります.

これは,対応する.cdfファイルの中で.pofファイルや.sofファイルへの

正しくパスが書かれていないのが原因です.

他のマシン等で作成したプロジェクトを持ってきた時に発生します.

解決方法(いずれかの方法を取ること)

- 対応する.cdfをメモ帳等のテキスト・エディタで開き,

"Device Part Name..."で始まる行のPathの項目を正しいパスに直す

- 新しいプロジェクトを作成し,そこに前のプロジェクトのファイルを持ってきてやり直す

- RAM作成時の設定で"Allow In-System Memory Content Editor..."を指定していない

- RAMをダブルクリックし,"Allow In-System Memory Content Editor..."を指定する

- USB-Blasterとの接続悪くてボードと通信できていない

- USB-Blasterとの接続を確認した後"Scan"を押す

- 通信中に途切れることもあります

実際の論理回路では,信号が論理ゲートを通過するに一定の時間がかかりますが,

機能シミュレーションではこの遅延時間を考慮せず,単純に論理の正しさのみを評価します.

このため,実際にはレジスタ(レジスタ・ファイルのみならず,一時的に値を保持するレジスタも含む)の

書き込み時にセットアップ時間やホールド時間を満たせない回路でも,

機能シミュレーションの上では動いてしまいます.

そこで,以下のように,コンパイル時のタイミング解析の結果を元に,

あやしい信号パスを見つけ,問題が発生しないように修正します.

※ 以下は Ver.9 までの Timing Analyzer の記述です.

新しい TimeQuest でも基本的には同じですが,回路性能の見方 のほうに追記します.

- コンパイルをする

- Compilation Report→Timing Analyzerを開き,その中の各項目に,

赤色で示される,タイミング違反の結果がないか探します.

- Clock Setup:

前段のレジスタへの出力が変更されてから(前段のレジスタにクロックの入力されてから),

その信号が論理回路を通過して,後段のレジスタへの入力に入るまでの時間

- Tsu: レジスタの入力のセットアップ時間

- Th: レジスタの入力のホールド時間

- Tco: チップ外への出力がある信号パスに対し,

前段のレジスタの出力が変更されてから,その信号が論理回路を通過して,

出力ピンまでに到達する時間

- Tpd: チップ外からの入力がある信号パスに対し,

入力ピンからの入力が変更されてから,その信号が論理回路を通過して,

レジスタの入力に入るまでの時間

- 問題となる信号パスが見つかりましたら,そのエントリ番号を左クリックし,

Locate→Locate in Technology Map ViewerもしくはRTL Viewerで表示させます

- すでにコンパイルされた結果をもとに表示するため,

Block Diagram Editor上の図とは異なります

- 遅延時間が短すぎる信号パスがあったら,適当な論理ゲートを入れて,

遅延時間を延ばしてタイミング制約を満たすという手があります

- ただし,あまりにも単純な素子だと,

コンパイラが最適化で取り除いてしまう可能性があります

- とりあえず,NOTゲートはだめだったが,

セレクタは大丈夫だったという報告があります

MegaFunction ALTPLLを使って下さい.

外部入力クロックのM/N倍のクロックを内部で作れます.

PLLを使うときは外部入力クロックは40MHzまたは20MHzにして下さい (遅いクロックでは変な動きになると思います).

ちなみに,このFPGAの動作周波数は275MHzぐらいが上限です.

- inkscape, LibreOffice Draw (lodraw) が使えると思います.

- ペイント系なら gimp が使えます.スクリーンショットや回路図に簡単な説明を加えるならこちら.

- tgif (1回生で使った?) で日本語を使いたい人は,このページなどを参照して設定して下さい.これでも入力メソッドがつながらなければ,フォントだけ指定して入力はカット&ペーストで.

- Quartus内ではプロジェクト管理の内部ファイルが多く生成されます.各人や合成毎に内容が違いますので,これをGit管理下にすると相方との仲が悪くなります(ソフトウェアのIDEでもそうですが)

- gitignoreを適切に設定しましょう.ググればいろいろ出てきますが,この辺りが有名なようです.

- Windowsの場合: C:\intelFPGA_lite\20.1\uninstall\quartus_lite-20.1.0.590-windows-uninstall.exe を実行

- Linuxの場合: ~/intelFPGA_lite/20.1/uninstall/quartus_lite-20.1.0.590-linux-uninstall.run を実行

- これ以外の方法(ディレクトリを全削除など)は後々の問題に繋がるので注意してください.

以下の内容を ~/.ssh/config に書いておくと自動的にプロキシサーバ経由の接続になります.

Host *

ProxyCommand nc -x socks-proxy.kuins.kyoto-u.ac.jp:1080 %h %p

Quartusの起動方法

Quartusの起動方法

Quartusの起動方法

Quartusの起動方法

コンパイルしようとするとライセンスがないと言われて止まる

コンパイルしようとするとライセンスがないと言われて止まる

シミュレーションしようとするとライセンスがないと言われて止まる

シミュレーションしようとするとライセンスがないと言われて止まる

ライブラリを開くなどの操作の際,ツールが固まって落ちるようになった

ライブラリを開くなどの操作の際,ツールが固まって落ちるようになった

MegaWizard が固まる

MegaWizard が固まる

Helpが見られない

Helpが見られない

Assignment→Pinsでピン指定に候補が出ない

Assignment→Pinsでピン指定に候補が出ない

Assignment→Pinsで異なるピンが候補に出る

Assignment→Pinsで異なるピンが候補に出る

コンパイル時に,コンパイルすべきファイルが

ない旨を表示して停止する

コンパイル時に,コンパイルすべきファイルが

ない旨を表示して停止する

バスの中の1本の線はどのように引き出すか

バスの中の1本の線はどのように引き出すか

バス間をつなぐ配線の名前のつけ方は?

バス間をつなぐ配線の名前のつけ方は?

波形シミュレーションでブロック図の途中の配線の値を見たい

波形シミュレーションでブロック図の途中の配線の値を見たい

ファイルが開けません

ファイルが開けません

CADがちゃんと動作していないようなのですが

CADがちゃんと動作していないようなのですが

他のプロジェクトで作った回路をインクルードしたい

他のプロジェクトで作った回路をインクルードしたい

CADのエラー・メッセージが分からない

CADのエラー・メッセージが分からない

正しくバス/配線/ファイル等に名前をつけているのにどうも正しく認識されていないようだ

正しくバス/配線/ファイル等に名前をつけているのにどうも正しく認識されていないようだ

タブ・バーを間違って消してしまい,戻し方がわからない

タブ・バーを間違って消してしまい,戻し方がわからない

タイミング制約のかけ方

タイミング制約のかけ方

回路性能の見方

回路性能の見方

組み合わせ回路の動作速度の見方

組み合わせ回路の動作速度の見方

デザインパーティション

デザインパーティション

GUIじゃやってられないんですけど

GUIじゃやってられないんですけど

実験時間内だけで実験を終わらせる自信がないのですが

実験時間内だけで実験を終わらせる自信がないのですが

最終報告までに完成させてデモをできなかったのですが

最終報告までに完成させてデモをできなかったのですが

グループ内でのファイルの受渡しはどうやればいいか

グループ内でのファイルの受渡しはどうやればいいか

コンピュータの問題から,設計データが消えてしまいました

コンピュータの問題から,設計データが消えてしまいました

途中からグループの相方が出てこなくなりました

途中からグループの相方が出てこなくなりました

D-フリップフロップにあるPRN入力の意味が分かりません

D-フリップフロップにあるPRN入力の意味が分かりません

各論理素子の動作が分からない(真理値表が見たい)

各論理素子の動作が分からない(真理値表が見たい)

アドレス・バスやデータ・バスで複数のレジスタからの値が混ざる

アドレス・バスやデータ・バスで複数のレジスタからの値が混ざる

RAMからデータが出てこない

RAMからデータが出てこない

SIMPLEの仕様に則って64kWのRAMを作ろうとすると合成エラーになる

SIMPLEの仕様に則って64kWのRAMを作ろうとすると合成エラーになる

LEDのダイナミック点灯とは何か

LEDのダイナミック点灯とは何か

FPGAボードの各モジュールが正常に動作しているか確認したい

FPGAボードの各モジュールが正常に動作しているか確認したい

USBでボードを接続するとドライバをインストールしろと言われる

USBでボードを接続するとドライバをインストールしろと言われる

WindowsでボードUSBケーブルのドライバが認識しない

WindowsでボードUSBケーブルのドライバが認識しない

LinuxでボードUSBケーブルのドライバが認識しない

LinuxでボードUSBケーブルのドライバが認識しない

設定と接続は正しいはずなのにProgrammerがFailedになる

設定と接続は正しいはずなのにProgrammerがFailedになる

設計した回路をFPGAにダウンロードしようとすると

"Can't recognize sillicon ID for device 1"と出てダウンロードできない

設計した回路をFPGAにダウンロードしようとすると

"Can't recognize sillicon ID for device 1"と出てダウンロードできない

FPGAへのダウンロード時のファイルで.pofファイルや.sofファイルを指定できない

FPGAへのダウンロード時のファイルで.pofファイルや.sofファイルを指定できない

In-System Memory Content EditorでRAMが出てこない

In-System Memory Content EditorでRAMが出てこない

機能シミュレーションではちゃんと動くのに,ボード上では動かない

機能シミュレーションではちゃんと動くのに,ボード上では動かない

40MHzより速いクロックで動かしたい

40MHzより速いクロックで動かしたい

レポートの図を書くソフトは?

レポートの図を書くソフトは?

Git管理でゴミファイルのconflictがやってられない(gitignore)

Git管理でゴミファイルのconflictがやってられない(gitignore)

Quartus Primeを自身のPCからアンインストールしたい

Quartus Primeを自身のPCからアンインストールしたい

演習室のPCから学外 (GitHub等) にSSHで接続できない

演習室のPCから学外 (GitHub等) にSSHで接続できない